在电子工程领域,尤其是涉及高速、高密度电路的设计中,电磁兼容性(EMC)已成为衡量产品可靠性的核心指标。业内常言“90%的EMC问题是设计出来的”,这句话深刻地揭示了EMC问题的根源——它们并非偶然产生,而是在设计阶段就埋下了伏笔。这一论断在集成电路(IC)设计中体现得尤为明显和关键。

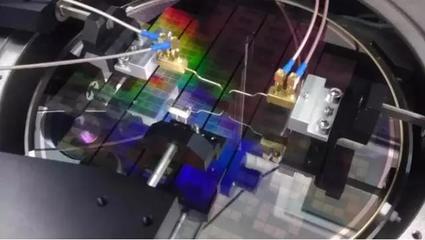

我们需要理解EMC的本质。EMC是指设备或系统在其电磁环境中能正常工作,且不对该环境中的任何其他设备构成无法承受的电磁干扰的能力。它包含两个方面:电磁干扰(EMI)和电磁抗扰度(EMS)。一旦芯片设计完成并流片生产,其物理结构、布线、电源分布、信号完整性等特性便已固化。后期通过外部屏蔽、滤波或布局调整来“修补”EMC问题,往往成本高昂、效果有限,且可能影响性能。因此,将EMC考量前置到芯片设计阶段,是最高效、最经济的策略。

具体到集成电路设计,以下几个关键环节直接决定了最终的EMC表现,也恰恰是“设计出来”的根源所在:

- 架构与电源规划:芯片的顶层架构和电源分配网络(PDN)设计是EMC的基石。糟糕的电源规划会导致严重的电源噪声(如地弹、电源轨道塌陷),这些噪声会通过电源引脚辐射出去或耦合到信号中,成为主要的干扰源。设计阶段对电源域划分、去耦电容的布置、电源网格阻抗的控制,直接决定了电源的纯净度。

- 时钟与高速信号设计:时钟信号通常是芯片中频率最高、边沿最陡的信号,是最大的潜在干扰源。设计时,时钟树的综合、布线(是否采用差分对、屏蔽层)、缓冲器插入策略,都会影响其谐波辐射。同样,高速数据总线(如DDR、SerDes)的拓扑、端接匹配、等长控制若不恰当,会产生信号完整性(SI)问题,如过冲、振铃和串扰,这些都会转化为电磁辐射。

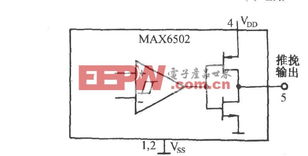

- 输入/输出(I/O)单元与封装:I/O驱动器是芯片与外部世界的接口,其驱动强度、压摆率控制、同时开关噪声(SSN)管理至关重要。过强的驱动或过快的边沿会产生丰富的谐波。封装的选择(如引线键合与倒装焊)、封装内的电源/地引脚分配、寄生电感电容,都会极大地影响芯片引脚处的噪声和辐射效率。这些必须在芯片-封装协同设计时就进行优化。

- 衬底耦合与内部噪声:在深亚微米工艺下,晶体管密度极高,通过公共硅衬底的噪声耦合(衬底噪声)成为一个严重问题。数字电路的开关噪声会通过衬底干扰敏感的模拟电路(如RF模块、PLL、ADC),导致性能下降。这需要通过设计合理的隔离结构(如深N阱、保护环)和物理布局隔离来缓解。

- 设计方法与工具:现代IC设计离不开EDA工具。在设计阶段利用EMC/SI分析工具进行预仿真,如电源完整性(PI)分析、信号完整性(SI)分析、以及近场辐射仿真,可以在流片前识别潜在热点。诸如“设计即正确”的方法学,强调通过设计规则检查(DRC)、电气规则检查(ERC)以及特定的EMC设计规则来规避问题。

因此,“90%的EMC问题是设计出来的”并非夸张。它强调的是一种预防性的哲学:与其在后期测试中耗费巨资进行整改和迭代,不如在成本投入最低、灵活性最高的设计初期,就系统性地将EMC作为一项核心设计约束。对于集成电路设计师而言,这意味着需要具备跨领域的知识,将系统级EMC要求转化为芯片级的物理和电气设计决策。

结论是,一颗EMC性能优良的芯片,必定是“精心设计出来”的。它从架构规划、电路实现、物理布局到封装选择,每一个环节都融入了对电磁能量的控制与管理。这正是EDA365等平台和社区强调设计重要性、推广先进设计方法与工具的意义所在——赋能设计师在源头扼杀EMC问题,打造出真正可靠、高性能的集成电路产品。