在当今高速发展的信息时代,集成电路的性能、功耗和可靠性已成为衡量芯片优劣的核心指标。随着工艺节点不断微缩,工作频率持续攀升,信号在芯片内部传输的时序问题变得愈发突出。传统的静态缺陷测试已无法全面覆盖动态性能失效,因此,时延可测性设计应运而生,成为现代集成电路设计流程中不可或缺的关键环节。

一、 时延故障与测试挑战

时延故障是指电路由于物理缺陷(如金属线开路、桥接、晶体管参数漂移等)或工艺波动,导致信号传播速度低于预期,无法在规定的时间窗口内达到稳定逻辑值,从而引发功能错误。这类故障是导致芯片在实际工作频率下失效的主要原因。与静态“固定型故障”不同,时延故障是动态的、与频率相关的,其测试面临巨大挑战:

- 测试向量生成复杂:需要精确控制信号的时序关系,生成双模式测试向量(Launch-On-Capture或Launch-On-Shift),以激活并捕获路径时延。

- 测试成本高昂:需要高速的测试设备(ATE)来施加高频测试时钟,且测试时间较长。

- 测试覆盖不全:芯片中存在海量的潜在关键路径,穷尽测试所有路径时延在经济和技术上均不可行。

二、 时延可测性设计的基本原理与方法

时延可测性设计通过在芯片设计阶段植入特定的硬件结构,增强对内部时序特性的控制和观测能力,从而高效、经济地完成时延测试。其主要方法包括:

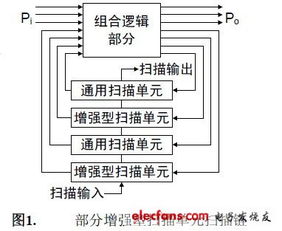

1. 扫描链增强设计

在标准扫描设计(DFT)基础上进行扩展:

- 多时钟域扫描:支持对异步时钟域路径的时延测试。

- 时钟控制逻辑:集成精确的时钟生成、选择和门控单元,以产生测试所需的高速脉冲和时序序列。

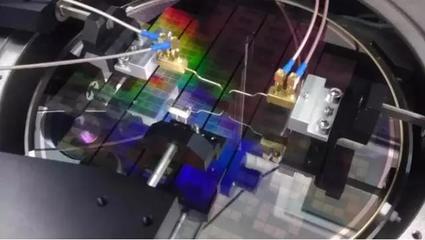

2. 内建自测试

- 时延BIST:在芯片内部集成测试模式生成器和响应分析器,通过片上环形振荡器或延迟线产生高频测试时钟,实现对关键路径的在线时延测量,大幅降低对外部ATE的依赖。

3. 路径与时延故障模型

- 关键路径选择与隔离:通过静态时序分析工具识别出对时序最敏感的关键路径,并在设计中有选择性地为其插入测试点(如观测触发器、控制多路器),确保这些路径能被测试向量有效激活和捕获。

- 过渡故障模型与路径时延模型:前者关注单个门电路的上升/下降延迟,后者关注整个组合逻辑路径的累积延迟,两者结合能更全面地刻画时延缺陷。

4. 片上时钟与控制网络

设计灵活、低偏斜的时钟分布网络,并集成可编程的时钟延迟单元和脉冲发生器,为时延测试提供精确、可调的时序基准。

三、 设计流程与权衡考量

将时延可测性设计融入标准IC设计流程(从RTL到GDSII)至关重要:

- 前端设计阶段:在RTL编码时考虑测试结构,规划时钟与复位架构。

- 综合与布局布线:在插入扫描链的考虑时延测试的布线约束,避免引入额外的关键路径。

- 签核与验证:进行带有时延测试模式的时序仿真和ATPG(自动测试向量生成)。

DFTD并非没有代价,设计者必须谨慎权衡:

- 面积开销:额外的逻辑(如多路器、触发器、控制电路)会增加芯片面积。

- 性能影响:插入的测试点可能增加关键路径的负载与延迟。

- 功耗增加:测试期间的高频切换活动会导致动态功耗显著上升。

- 设计复杂度:增加了验证和物理实现的难度。

四、 未来发展趋势

随着工艺进入纳米尺度及三维集成电路、异质集成等新技术的发展,时延可测性设计面临新机遇与挑战:

- 与自适应调频调压技术结合:测试结果可用于指导芯片的实时频率-电压调整,提升能效与可靠性。

- 机器学习辅助:利用AI算法预测关键路径、优化测试向量集,提升测试效率与覆盖率。

- 面向先进封装:解决芯粒间互连的时延测试与监控问题。

- 在线监测与预测性维护:将时延监测电路作为永久性IP嵌入系统,实现芯片生命周期内的健康状态追踪与失效预警。

###

总而言之,时延可测性设计是连接芯片设计卓越性与制造可靠性的核心桥梁。它通过前瞻性的设计投入,将难以捉摸的动态时序缺陷转化为可管理、可测试的工程问题,从而确保高性能集成电路在目标频率下稳定工作。面对日益严峻的时序收敛挑战和更高的质量要求,深入研究和应用先进的时延可测性设计技术,对于提升我国集成电路产业的整体竞争力具有重要的战略意义。